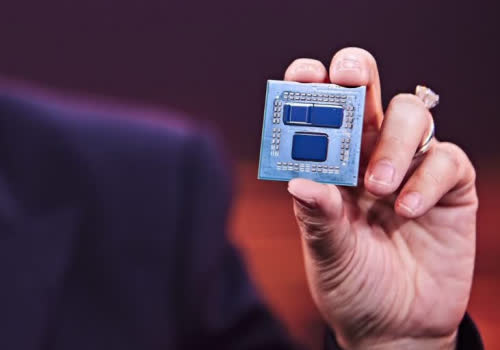

Developed in collaboration with TSMC, AMD’s first application of the 3D chiplet tech is a vertical cache addition for its high-end processors. In a nutshell, AMD used a process called through-silicon vias (TSVs) to stack additional L3 cache on top of the compute chiplets.

from TechSpot

Read The Rest:techspot...

No comments:

Post a Comment